A = b >> c;シフト演算 a > 3;シフト演算中に符号を保持します。 forループの後に、シフトされた値の符号を設定する必要があります。 このような何かが動作することができる:左側から挿入されているすべての 桁がシフトされていない値、すなわち unshiftedwidth1 の符号ビットに等しくなければならない こと

Opencores By Verilog Source With Vhdl Translation

Verilog シフト演算子 合成

Verilog シフト演算子 合成-シフト演算は論理資源を消費しませんので、多数項を加算する際の効率が乗算器の性能を決めます。 Verilogで加算を行うには"a b"などのようにすればよく、多数の項を加算したい場合は"a b c d "という書き方もできます。Assign Y = CalcY (S, M, A, B, C);

問題11 パラメタライズによる回路の記述 完全マスター 電子回路ドリル Iii 11 Monoist

0 SystemVerilog VerilogのUnarrayシフト演算子ですか?1 systemverilogで 'net'データ型を使用する必要がある場合は何ですか? 0 SystemVerilogのオンザフライで変数名を変更;シフト演算 VHDLと異なり,Verilog HDLにはシフト演算子がありますが,シフト演算は大きな回路になってしまいます. 定数分のシフトを行いたい場合は,配列の結合演算を用いて実装する方が小さな回路として実現できます.除算アルゴリズム 復元法 除算のアルゴリズムは、人間が筆算で行う除算と同じである。 すなわち、桁を合わせながら除数と被除数を比較し、除数が被除数以下ならば商にビット1を立てるとともに被除数から除数を引く(引き算を行う)。

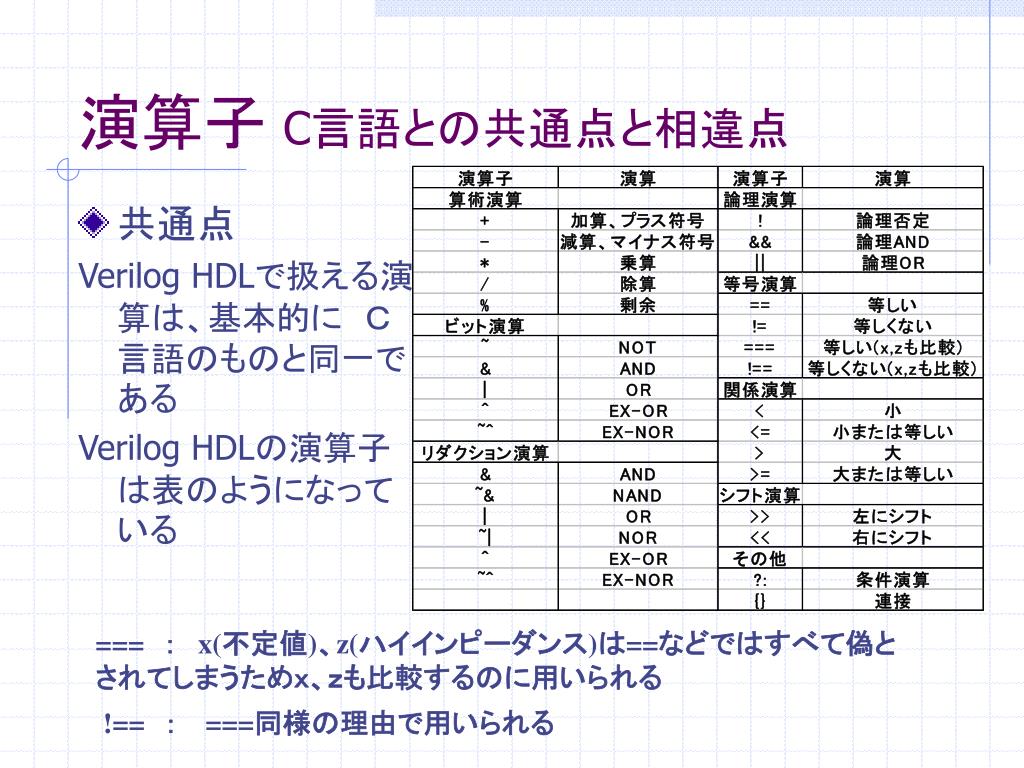

Assign parity_bit = ^data;Verilog‐HDL 簡易文法書 基数の表記が異なるものでも演算可能。 ・ シフト演算子 演算子 意味 > 右シフト 4 <module の入出力宣言>// 3bit Verilogの処理系のエラーメッセージはお世辞にもわかりやすいとは言えません. 例えば,以下のような32ビットの加算を行うモジュールを考えてみます.

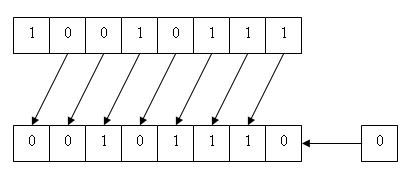

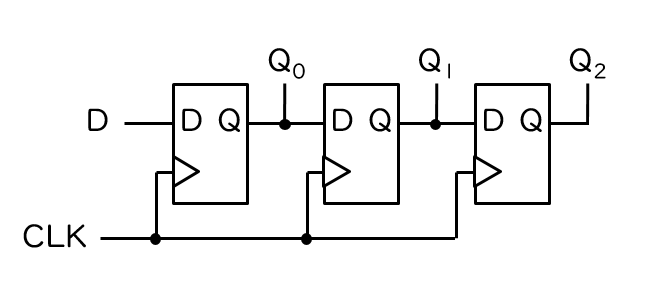

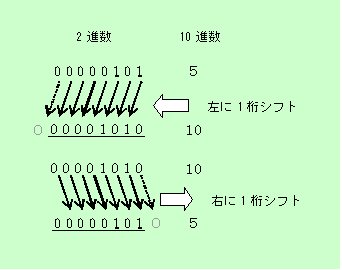

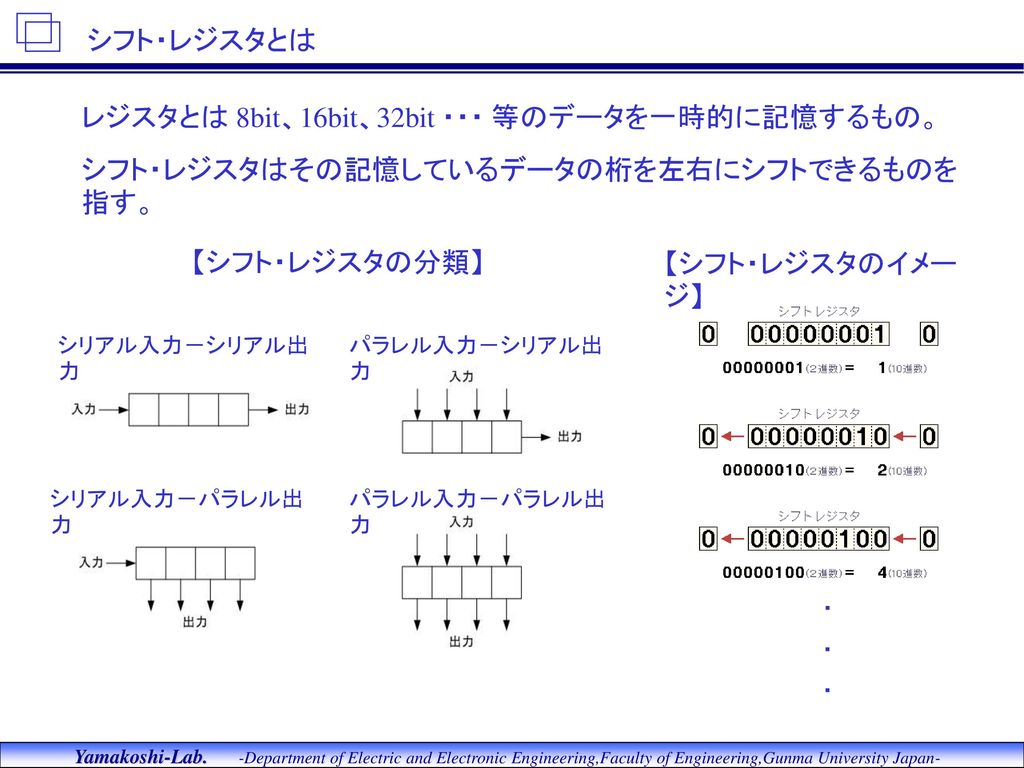

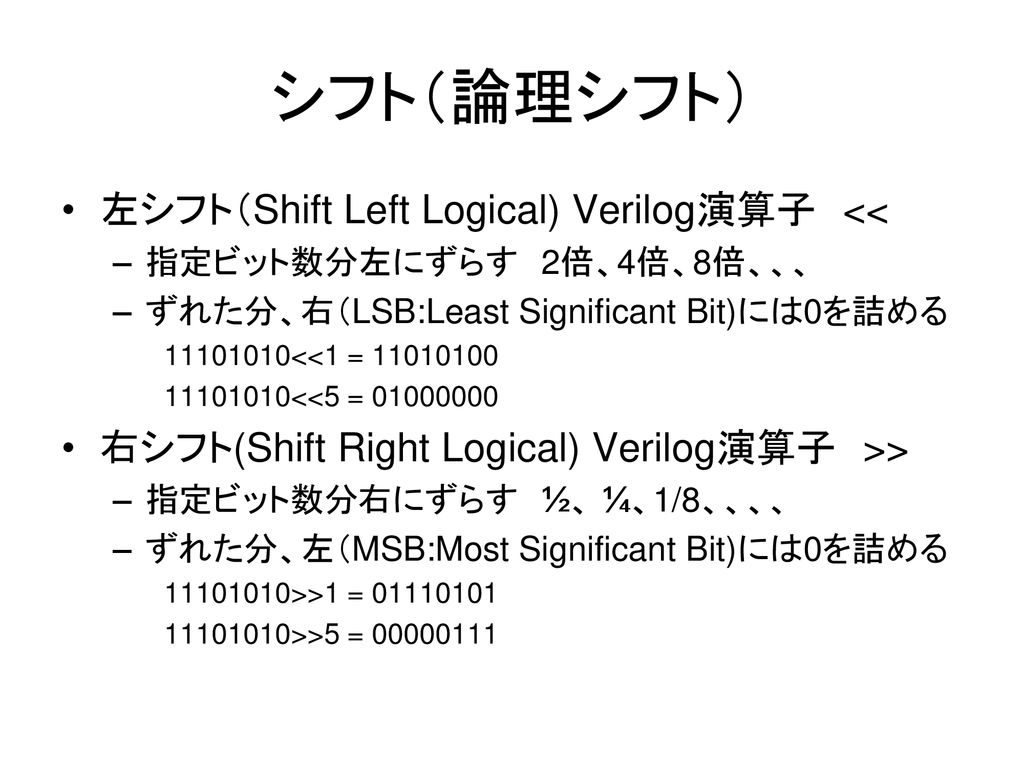

左辺の信号を、右辺で指定されたビット数分だけ論理シフトする。 例えば、data = 8'b のとき、dataシフト演算子は、各ビットの値を左や右にシフトさせます。 左シフトは MSB 側にシフトされ、LSB 側には 0 が補充されます。 逆に右シフトは LSB 側にシフトされ、MSB 側には 0 が補充されます。シフトレジスタ 基本的にはDFFの記述と同じです。算術演算 これをVerilogHDLで記述する方法は幾つかありますが、ここではcase文を使用して記述してみます。

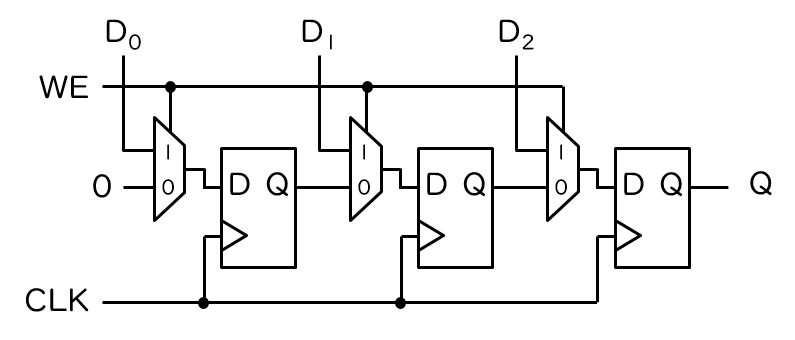

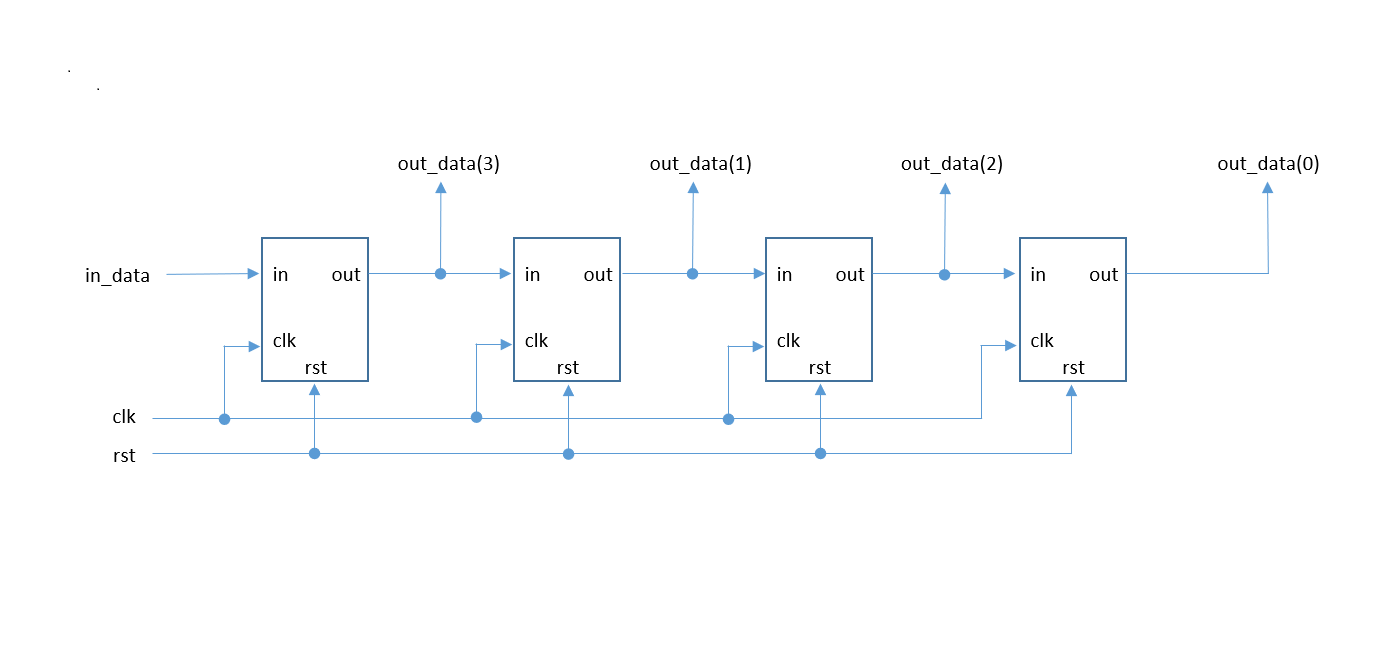

情報画像学実験ii 実験1 論理回路

情報画像学実験ii 実験1 論理回路

End end endfunction wire S, M;シフトレジスタ 基本的にはDFFの記述と同じです。算術演算 これをVerilogHDLで記述する方法は幾つかありますが、ここではcase文を使用して記述してみます。== 等しくない(x,zも比較) < 小さい 大きい >= 以上 算術演算 加算 減算 乗算 = 除算 % 剰余算

情報画像学実験ii 実験1 論理回路

情報画像学実験ii 実験1 論理回路

Verilog‐HDL 簡易文法書 基数の表記が異なるものでも演算可能。 ・ シフト演算子 演算子 意味 > 右シフト 4 <module の入出力宣言>Input 30 A, B, C;とすると、aは7fになる これをffにしたいときは a = b >>> c;

Systemverilog文法メモ Kivantium活動日記

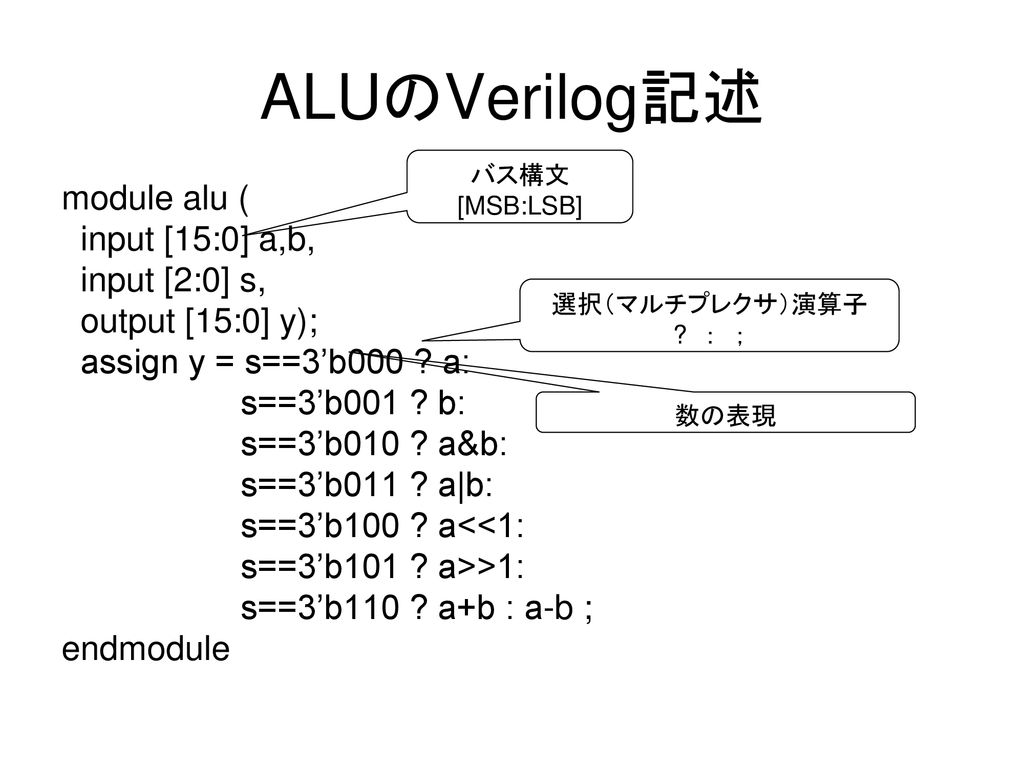

計算機構成 第2回 Aluと組み合わせ回路の記述 Ppt Download

シフト演算 右オペランド分左シフト(空いたビットは0) 4 >> 右オペランド分右シフト(空いたビットは0) 4 条件演算?Verilogでの算術シフト ハブ君の寝言 シフトは a = b >> c;Wire 30 A, B, C;

情報画像学実験ii 実験1 論理回路

Fpga Tutorial 演習問題を解きながら理解しようと 演習2 4ビット乗算器 Verlog Hdの基礎の基礎

// 下記と等価です // assign parity_bit = data 3 ^ data 2 ^ data 1 ^ data 0;とするだけでいい今までなんでわざわざ符号拡張するコードを書いていたのか dhatenanejp dhatenanejp この記事では、 >>> を使用すれば、算術シフト、 >> を使用すれば論理シフトになるかのようにここで Verilog の論理式の書き方をまとめておく。 C 言語と似ているのでマニュアルを見なくても大体想像がつくが、ハードウェアを記述するためにビット単位の書き方になっている点が特徴である。 変数 ・ reg 変数でも wire 変数でも必ずビット幅を指定して宣言する。

C言語入門 ビット演算子 シフト演算子の使い方 使い道も解説 侍エンジニアブログ

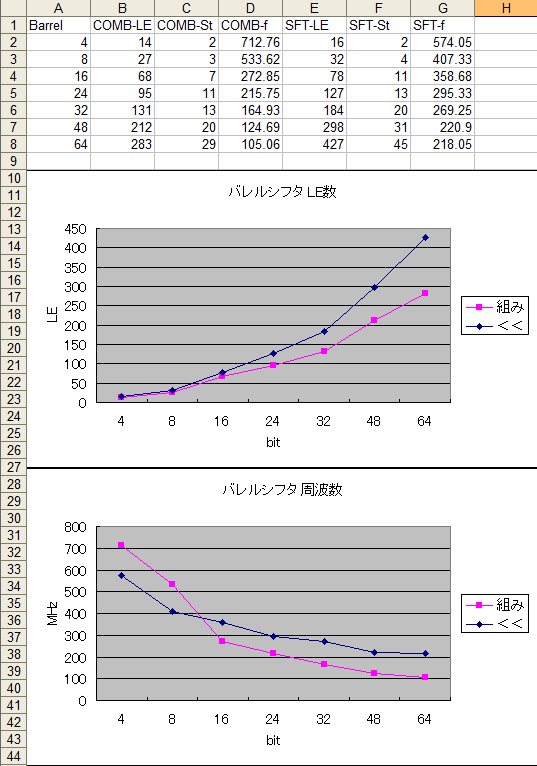

Quartusii 12 1 バレルシフタの記述比較 まごころせいじつ堂

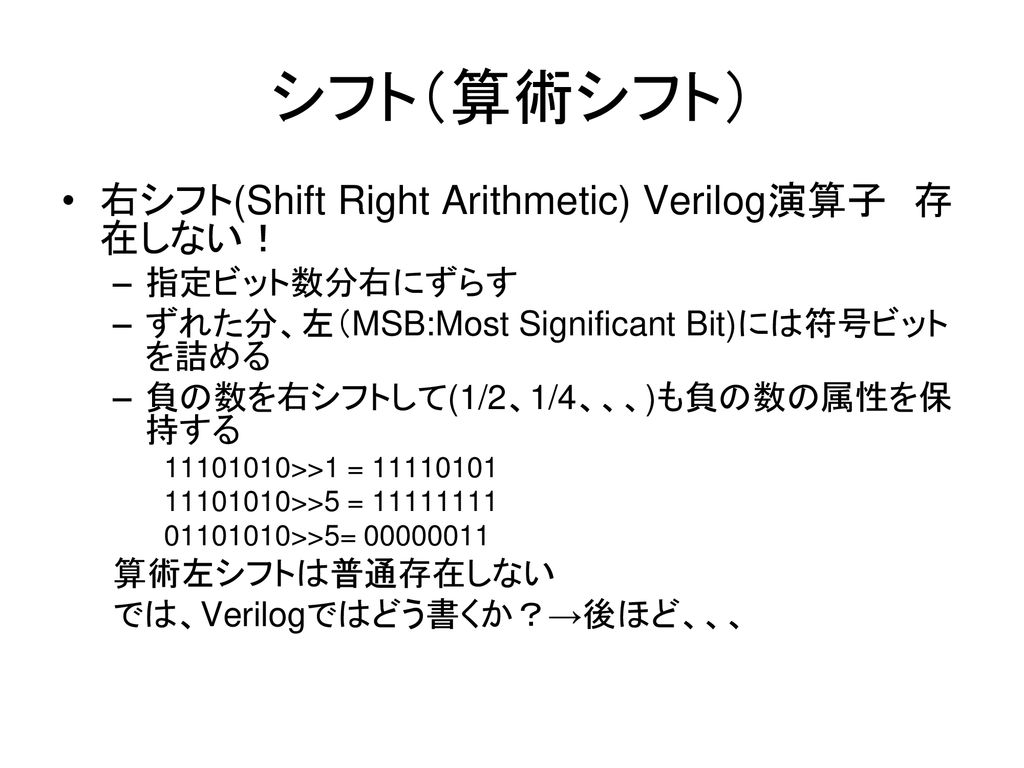

End end else begin CalcY = C;= 等しくない === 等しい(x,zも比較)!シフト(論理シフト) •左シフト(Shift Left Logical) Verilog演算子

シフト演算

Int34 C 負のビット数のシフトやオペランドのビット数以上のシフトを行わない

演算を行い、結果は1bit で返ります。 ┌─────────────────────────────────────┐ reg 30 data;条件?真の場合の結果偽の場合の結果 11 連接 {,} 二つ以上のオペランドをひとつのビット表現にまとめるシフト演算子はビット演算子の一つで数値の各ビットを左又は右へシフトさせるための演算子です。 シフト演算子だけもう一度確認してみます。 演算子 記述例

Verilog Hdlで算術右シフトを書く方法 Var Log Hikalium

Systemverilog文法メモ Kivantium活動日記

Begin if ( S == 1'b0 ) begin if ( M == 1'b0 ) begin CalcY = A;表1 Verilogの基本的演算子 ビット演算 ~ NOT & AND ~& NAND j OR ~j NOR ^ ExOR ~^ ExNOR シフト演算 > 右シフト 等号、関係演算 == 等しい!End else begin CalcY = B;

問題11 パラメタライズによる回路の記述 完全マスター 電子回路ドリル Iii 11 Monoist

Fpgaで信号処理 符号なし整数除算器の高速化

でいいのだが wire 70 a,b,c;2 項演算 a op b のビット幅の解釈 (1) a と b のビット幅は大きい方に合わせてゼロ拡張する。 ただし a,b 両方が符号つきであれば、ゼロでなく符号拡張する。 (2) 演算結果は (1) のビット幅に合わせる。 ただし代入文では左辺の幅に合わせる。 例) 演算結果自体ビット演算子「シフト」 シフト演算子はビット配列をずらす演算子です。 >> 変数a → となります。

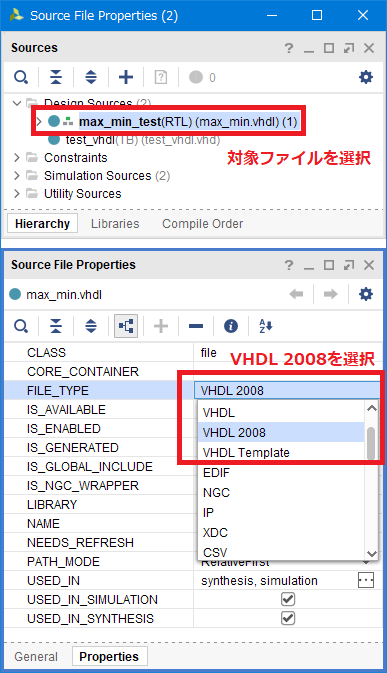

Vivadoでのvhdl 08サポート Qiita

Fpga Tutorial 演習問題を解きながら理解しようと 演習2 4ビット乗算器 Verlog Hdの基礎の基礎

(アセンブラ表記が違っても、マシンコードが同じであるように) >>>シフト演算子は、第一パラメータがsignedであるときだけ算術シフト動作を行い、unsigned のときは、>>(論理シフト)と同じ動作になります。 なお、Rotational演算子は、Verilogではありません。

Opencores By Verilog Source With Vhdl Translation

Verilog Hdlでの回路記述で用いる数値表現と演算子 授業用 Qiita

シリアル通信で Hello Fpga 1 Acri Blog

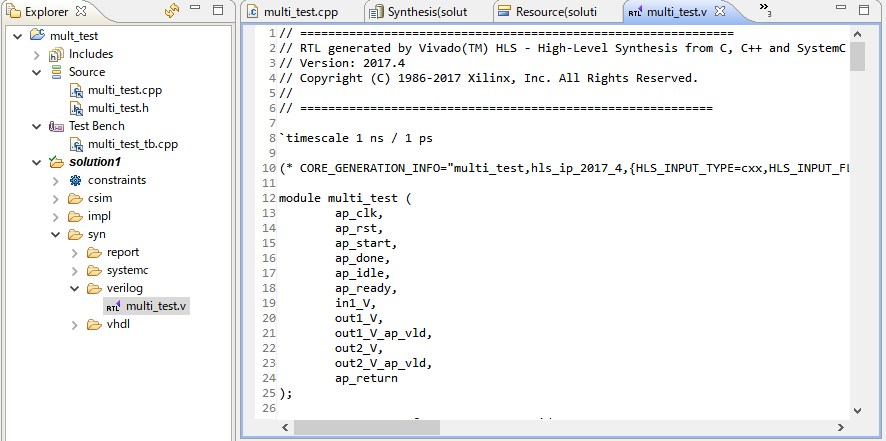

Vivado Hls 17 4 で片方が定数の場合の乗算の検討2 C コードの合成1 Fpgaの部屋

初めてでも使えるverilog Hdl文法ガイド 記述スタイル編 Tech Village テックビレッジ Cq出版株式会社

Verilog Hdl デザイン テンプレート パブー 電子書籍作成 販売プラットフォーム

Verilog Hdl 入門編トライアル コース テキスト Pdf 無料ダウンロード

情報画像学実験ii 実験1 論理回路

5 3 各種カウンタ 平木 Ppt Download

Hdlてにをは集

計算機構成 第2回 Aluと組み合わせ回路の記述 Ppt Download

情報画像学実験ii 実験1 論理回路

情報画像学実験ii 実験1 論理回路

もう一度基礎からc言語 第19回 いろいろな演算子 ビット演算子 ビット演算子

みやを 算術左シフト Sla Alu Op Type 4 と論理右シフト Sra Alu Op Type 5 のケース Verilog Hdlの算術シフト演算子 変数 Reg Wire をsigned宣言か Signedでキャストしてないと論理シフト と動作が変わらないって わかりにくすぎる

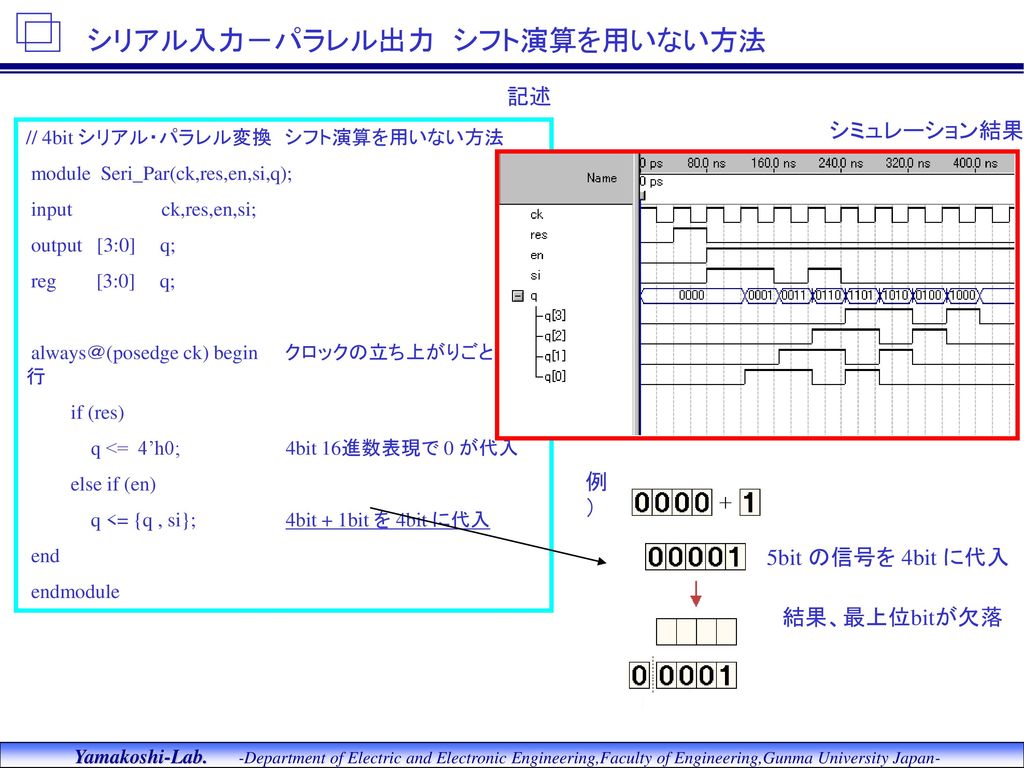

改訂 入門verilog Hdl記述

5 3 各種カウンタ 平木 Ppt Download

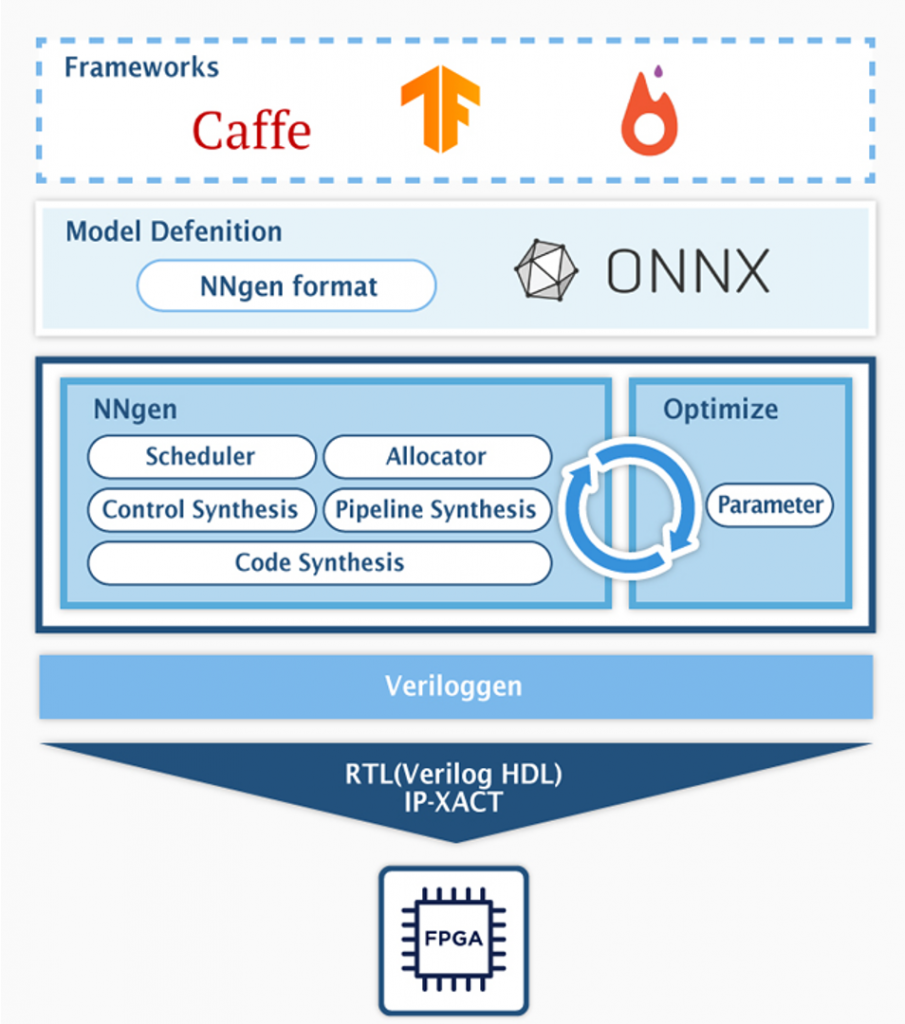

Nngen と Fpga で作るニューラルネットワーク アクセラレータ 1 Acri Blog

覚え書き Verilog 乗算器

実習 ディープラーニング ハードウェア化への道 Cq出版株式会社

初めてでも使えるverilog Hdl文法ガイド 文法ガイド編 Tech Village テックビレッジ Cq出版株式会社

計算機構成 第2回 Aluと組み合わせ回路の記述 Ppt Download

Fpgaの信号処理論理 シフトと定数乗算

絶版06 7 16 Verilog Hdl 論理合成入門

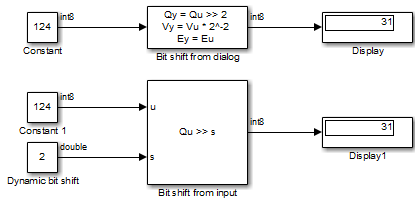

信号のビットや 2 進数小数点をシフト Simulink Mathworks 中国

初めてでも使えるverilog Hdl文法ガイド 記述スタイル編 Tech Village テックビレッジ Cq出版株式会社

計算機構成 第2回 Aluと組み合わせ回路の記述 Ppt Download

複雑な演算子

シフト演算

問題11 パラメタライズによる回路の記述 完全マスター 電子回路ドリル Iii 11 Monoist

シフト演算

Ppt 第 3 章 文法概略と基本記述スタイル Powerpoint Presentation Id

情報画像学実験ii 実験1 論理回路

コンピュータアーキテクチャ 7

信号のビットや 2 進数小数点をシフト Simulink Mathworks 中国

Verilog Hdl高度なf A Q Verilog Hdl は 謎めいた難解な言語です ときとして 言語に仕掛けられた呪文 罠により壮大な迷宮にはまり込んでしまうことがあるかもしれません ささやかながらお手伝いできたら幸いです Q1 Verification Ipを設計する

シリアル通信で Hello Fpga 1 Acri Blog

たまごの電子工作メモ 6月 12

Fpga Tutorial 演習問題を解きながら理解しようと 演習2 4ビット乗算器 Verlog Hdの基礎の基礎

初めてでも使えるverilog Hdl文法ガイド 記述スタイル編 Tech Village テックビレッジ Cq出版株式会社

シフト演算

情報画像学実験ii 実験1 論理回路

Fpgaの信号処理論理 シフトと定数乗算

演算子 C言語入門 It専科

問題 Verilog 記述式1 日経クロステック Xtech

たまごの電子工作メモ 6月 12

Verilog Formal Syntax Specification

Verilog Hdlで算術右シフトを書く方法 Var Log Hikalium

E4ilfokggdzvam

Hdlてにをは集

信号のビットや 2 進数小数点をシフト Simulink Mathworks 中国

Sfl Manual

No comments:

Post a Comment